XOR -port - XOR gate

| Input | Produktion | |

| EN | B | A XOR B |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

XOR -gate (undertiden EOR eller EXOR og udtales som Exclusive OR ) er en digital logisk gate, der giver et sandt (1 eller HIGH) output, når antallet af sande input er ulige. En XOR -port implementerer en eksklusiv eller ( ) matematisk logik ; det vil sige et sandt output, hvis en og kun en af inputene til porten er sand. Hvis begge input er falske (0/LOW) eller begge er sande, resulterer der i en falsk output. XOR repræsenterer ulighedsfunktionen, dvs. output er sandt, hvis input ikke er ens, ellers er outputtet falsk. En måde at huske XOR på er "skal have det ene eller det andet, men ikke begge dele".

XOR kan også ses som tillæg modulo 2. Som et resultat, XOR porte anvendes til at implementere binær tilføjelse i computere. En halv adder består af en XOR -port og en AND -port . Andre anvendelser omfatter subtraktorer, komparatorer og kontrollerede omformere.

De algebraiske udtryk eller eller alle betegner XOR-porten med input A og B . XOR's adfærd er opsummeret i sandhedstabellen vist til højre.

Symboler

Der er tre skematiske symboler for XOR -porte: de traditionelle ANSI- og DIN -symboler og IEC -symbolet. I nogle tilfælde bruges DIN -symbolet med ⊕ i stedet for ≢. For flere oplysninger se Logic Gate -symboler .

|

|

|

||

| ANSI XOR skematisk symbol | IEC XOR skematisk symbol | DIN XOR skematisk symbol |

De logiske symboler ⊕, J pq og ⊻ kan bruges til at betegne en XOR -operation i algebraiske udtryk.

C-lignende sprog bruger caret- symbolet ^ til at betegne bitvis XOR. (Bemærk, at tegnet ikke angiver logisk konjunktion (AND) på disse sprog, på trods af symbolets lighed.)

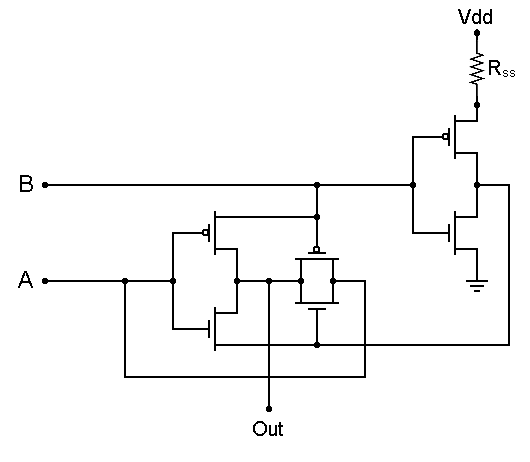

Pass-gate-logik ledninger

En XOR -port kan konstrueres ved hjælp af MOSFET'er . Her er et diagram over en pass transistor logisk implementering af en XOR -gate.

Bemærk: "Rss" -modstanden forhindrer shuntingstrøm direkte fra "A" og "B" til udgangen. Uden det, hvis kredsløbet, der leverer input A og B, ikke har den korrekte køreevne, vil output muligvis ikke svinge skinne til skinne eller være stærkt begrænset. "Rss" -modstanden begrænser også strømmen fra Vdd til jord, som beskytter transistorer og sparer energi, når transistorer overgår mellem tilstande.

Analytisk repræsentation

er en analytisk fremstilling af XOR gate:

er en alternativ analytisk repræsentation.

Alternativer

Hvis en bestemt type gate ikke er tilgængelig, kan et kredsløb, der implementerer den samme funktion, konstrueres ud fra andre tilgængelige porte. Et kredsløb, der implementerer en XOR -funktion, kan trivielt konstrueres ud fra en XNOR -port efterfulgt af en NOT -port . Hvis vi overvejer udtrykket , kan vi konstruere et XOR -gate -kredsløb direkte ved hjælp af AND, OR og NOT -porte . Denne fremgangsmåde kræver imidlertid fem porte af tre forskellige slags.

Som alternativ, hvis forskellige porte er tilgængelige, kan vi anvende boolsk algebra til at transformere som angivet ovenfor og anvende de Morgans lov til det sidste udtryk for at få, som kan implementeres ved hjælp af kun tre porte som vist til højre.

Et XOR -portkredsløb kan laves fra fire NAND -porte . Faktisk er både NAND- og NOR-porte såkaldte "universelle porte", og enhver logisk funktion kan konstrueres ud fra enten NAND-logik eller NOR-logik alene. Hvis de fire NAND -porte erstattes af NOR -porte , resulterer dette i en XNOR -port , som kan konverteres til en XOR -port ved at vende udgangen eller en af indgangene (f.eks. Med en femte NOR -port ).

| Ønsket port | NAND konstruktion | NOR konstruktion |

|---|---|---|

|

|

|

Et alternativt arrangement er fem NOR-porte i en topologi, der understreger konstruktionen af funktionen ud fra de Morgans lov og bemærker, at en NOR-gate er en inverteret input OG gate . Et andet alternativt arrangement er fem NAND-porte i en topologi, der understreger konstruktionen af funktionen ud fra de Morgans lov og bemærker, at en NAND-gate er en inverteret input ELLER-gate .

| Ønsket port | NAND konstruktion | NOR konstruktion |

|---|---|---|

|

|

|

For NAND -konstruktionerne kræver det øvre arrangement færre porte. For NOR -konstruktionerne giver det lavere arrangement fordelen ved en kortere udbredelsesforsinkelse (tidsforsinkelsen mellem en inputskift og outputændringen).

Mere end to input

Bogstavelig fortolkning af navnet "eksklusiv eller" eller observation af IEC -rektangulære symbol rejser spørgsmålet om korrekt adfærd med yderligere input. Hvis en logisk gate skulle acceptere tre eller flere input og producere et sandt output, hvis nøjagtigt et af disse input var sandt, ville det i virkeligheden være en en-hot detektor (og det er faktisk kun tilfældet for to input). Det er imidlertid sjældent implementeret på denne måde i praksis.

Det er mest almindeligt at betragte efterfølgende input som anvendt gennem en kaskade af binær eksklusiv-eller operationer: de to første signaler føres ind i en XOR-gate, derefter sendes output fra denne gate til en anden XOR-gate sammen med det tredje signal , og så videre for eventuelle resterende signaler. Resultatet er et kredsløb, der udsender et 1, når antallet af 1s ved dets indgange er ulige, og et 0, når antallet af indgående 1'er er lige. Dette gør det praktisk nyttigt som en paritetsgenerator eller en modulo-2 adder .

F.eks. Annonceres 74LVC1G386- mikrochippen som en logikport med tre input og implementerer en paritetsgenerator.

Ansøgninger

XOR-porte og OG-porte er de to mest anvendte strukturer i VLSI- applikationer.

Bruger derudover

XOR-logikporten kan bruges som en en-bit adder, der tilføjer to bits sammen for at udsende en bit. For eksempel, hvis vi tilføjer 1 plus 1 i binært , forventer vi et to-bit svar, 10 (dvs. 2 i decimal). Da den efterfølgende sumbit i denne output opnås med XOR, beregnes den foregående bærebit med en AND -gate . Dette er hovedprincippet i Half Adders . Et lidt større Full Adder -kredsløb kan være lænket sammen for at tilføje længere binære tal.

Pseudo-tilfældig talgenerator

Pseudo-random number (PRN) generatorer, specifikt lineære feedback skiftregistre (LFSR) , er defineret i form af den eksklusive eller operation. Derfor kan en passende opsætning af XOR -porte modellere et lineært feedback -skiftregister for at generere tilfældige tal.

Korrelation og sekvensdetektering

XOR -porte producerer et 0, når begge input matcher. Når man søger efter et specifikt bitmønster eller PRN -sekvens i en meget lang datasekvens, kan en række XOR -porte bruges til at sammenligne en streng af bits fra datasekvensen mod målsekvensen parallelt. Antallet af 0 udgange kan derefter tælles for at bestemme, hvor godt datasekvensen matcher målsekvensen. Korrelatorer bruges i mange kommunikationsenheder såsom CDMA -modtagere og dekodere til fejlkorrektion og kanalkoder. I en CDMA -modtager bruges korrelatorer til at ekstrahere polariteten af en specifik PRN -sekvens ud af en kombineret samling af PRN -sekvenser.

En korrelator, der leder efter 11010 i datasekvensen 1110100101, ville sammenligne de indgående databit mod målsekvensen ved hver mulig forskydning, mens antallet af kampe (nuller) tælles:

1110100101 (data)

11010 (target)

00111 (XOR) 2 zero bits

1110100101

11010

00000 5 zero bits

1110100101

11010

01110 2 zero bits

1110100101

11010

10011 2 zero bits

1110100101

11010

01000 4 zero bits

1110100101

11010

11111 0 zero bits

Matches by offset:

.

: :

: : : : :

-----------

0 1 2 3 4 5

I dette eksempel sker den bedste match, når målsekvensen er forskudt med 1 bit, og alle fem bits matcher. Når den er forskudt med 5 bits, matcher sekvensen nøjagtigt dens inverse. Ved at se på forskellen mellem antallet af ener og nuller, der kommer ud af bredden af XOR -porte, er det let at se, hvor sekvensen opstår, og om den er omvendt eller ej. Længere sekvenser er lettere at opdage end korte sekvenser.

Se også

- Eksklusiv eller

- OG port

- ELLER port

- Inverter (IKKE port)

- NAND port

- NOR -port

- XNOR port

- IMPLY gate

- Boolsk algebra

- Logisk port