Intel 8086 - Intel 8086

En sjælden Intel C8086-processor i lilla keramisk DIP-pakke med sidelodede stifter

| |

| Generelle oplysninger | |

|---|---|

| Lanceret | 1978 |

| Udgået | 1998 |

| Fælles producent (er) | |

| Ydeevne | |

| Maks. CPU -urfrekvens | 5 MHz til 10 MHz |

| Databredde | 16 bits |

| Adressebredde | 20 bits |

| Arkitektur og klassificering | |

| Min. funktionens størrelse | 3 µm |

| Instruktionssæt | x86-16 |

| Fysiske specifikationer | |

| Transistorer | |

| Co-processor | Intel 8087 , Intel 8089 |

| Pakke (r) | |

| Stikdåser | |

| Produkter, modeller, varianter | |

| Variant (er) | |

| Historie | |

| Forgænger | Intel 8085 |

| Efterfølger | 80186 og 80286 (som begge blev introduceret i begyndelsen af 1982) |

Den 8086 (også kaldet iAPX 86 ) er en 16-bit mikroprocessor chip designet af Intel mellem tidlig 1976 og juni 8, 1978, da det blev udgivet. Den Intel 8088 , Udgivet July 1, 1979 er en let modificeret chip med en ekstern 8-bit databus (tillade brugen af billigere og færre understøttende ICS ), og er bemærkelsesværdig, da den processor, der anvendes i den oprindelige IBM PC design.

8086 gav anledning til x86 -arkitekturen, som til sidst blev Intels mest succesrige serie af processorer. Den 5. juni 2018 udgav Intel en CPU i begrænset oplag, der fejrer 40-årsdagen for Intel 8086, kaldet Intel Core i7-8086K .

Historie

Baggrund

I 1972 lancerede Intel 8008 , den første 8-bit mikroprocessor. Det implementerede et instruktionssæt designet af Datapoint Corporation med programmerbare CRT-terminaler i tankerne, hvilket også viste sig at være temmelig generelt. Enheden havde brug for flere ekstra IC'er til at producere en funktionel computer, dels på grund af at den var pakket i en lille 18-benet "hukommelsespakke", hvilket udelukkede brugen af en separat adressebus (Intel var primært en DRAM- producent på det tidspunkt ).

To år senere lancerede Intel 8080 med de nye 40-pin DIL-pakker, der oprindeligt blev udviklet til lommeregner- IC'er for at muliggøre en separat adressebus. Det har et udvidet instruktionssæt, der er kildekompatibelt (ikke binært kompatibelt ) med 8008 og indeholder også nogle 16-bit instruktioner for at gøre programmeringen lettere. 8080-enhed blev til sidst erstattet af depletion-load baserede 8085 (1977), der tilstrækkeligt med en enkelt +5 V strømforsyning i stedet for de tre forskellige driftsspændinger af tidligere chips. Andre velkendte 8-bit mikroprocessorer, der opstod i løbet af disse år, er Motorola 6800 (1974), General Instrument PIC16X (1975), MOS Technology 6502 (1975), Zilog Z80 (1976) og Motorola 6809 (1978).

Det første x86 -design

8086 -projektet startede i maj 1976 og var oprindeligt tænkt som en midlertidig erstatning for det ambitiøse og forsinkede iAPX 432 -projekt. Det var et forsøg på at henlede opmærksomheden fra de mindre forsinkede 16- og 32-bit processorer fra andre producenter (f.eks. Motorola , Zilog og National Semiconductor ) og på samme tid at imødegå truslen fra Zilog Z80 (designet af tidligere Intel -medarbejdere), hvilket blev meget vellykket. Både arkitekturen og den fysiske chip blev derfor udviklet ret hurtigt af en lille gruppe mennesker og ved hjælp af de samme grundlæggende mikroarkitekturelementer og fysiske implementeringsteknikker som anvendt til den lidt ældre 8085 (og for hvilken 8086 også ville fungere som en fortsættelse) .

8086, der blev markedsført som kildekompatibel , var designet til at tillade samlingssprog til 8008, 8080 eller 8085 automatisk at blive konverteret til ækvivalent (suboptimal) 8086 kildekode, med lidt eller ingen håndredigering. Programmeringsmodellen og instruktionssættet er (løst) baseret på 8080 for at gøre dette muligt. 8086-designet blev dog udvidet til at understøtte fuld 16-bit-behandling.

Nye slags instruktioner blev også tilføjet; fuld understøttelse af signerede heltal, base+offset -adressering og selv -gentagende operationer lignede Z80 -designet, men blev alle gjort lidt mere generelle i 8086. Instruktioner, der direkte understøtter indlejrede ALGOL -familiesprog som Pascal og PL/M var også tilføjet. Ifølge hovedarkitekt Stephen P. Morse var dette et resultat af en mere software-centreret tilgang end i designet af tidligere Intel-processorer (designerne havde erfaring med at arbejde med kompilatorimplementeringer). Andre forbedringer omfattede mikrokodede multiplikations- og opdelingsinstruktioner og en busstruktur, der er bedre tilpasset fremtidige coprocessorer (såsom 8087 og 8089 ) og multiprocessorsystemer.

Den første revision af instruktionssættet og arkitekturen på højt niveau var klar efter cirka tre måneder, og da næsten ingen CAD -værktøjer blev brugt, arbejdede fire ingeniører og 12 layoutfolk samtidigt på chippen. 8086 tog lidt mere end to år fra idé til arbejdende produkt, hvilket blev betragtet som temmelig hurtigt for et komplekst design i 1976–1978.

8086 blev sekventeret ved hjælp af en blanding af tilfældig logik og mikrokode og blev implementeret ved hjælp af tømning-belastning nMOS kredsløb med cirka 20.000 aktive transistorer (29.000 tæller alle ROM- og PLA- steder). Det blev hurtigt flyttet til en ny raffineret nMOS -fremstillingsproces kaldet HMOS (til højtydende MOS), som Intel oprindeligt udviklede til fremstilling af hurtige statiske RAM -produkter. Dette blev efterfulgt af HMOS-II, HMOS-III-versioner og til sidst en fuldstændig statisk CMOS- version til batteridrevne enheder, fremstillet ved hjælp af Intels CHMOS- processer. Den originale chip målte 33 mm² og minimum funktionsstørrelse var 3,2 μm.

Arkitekturen blev defineret af Stephen P. Morse med lidt hjælp fra Bruce Ravenel (arkitekten i 8087) til at forfine de sidste revisioner. Logikdesigner Jim McKevitt og John Bayliss var ledende ingeniører på hardware-niveau udviklingsteamet og Bill Pohlman leder for projektet. Arven fra 8086 er vedvarende i det grundlæggende instruktionssæt for nutidens personlige computere og servere; 8086 lånte også sine to sidste cifre til senere udvidede versioner af designet, såsom Intel 286 og Intel 386 , som alle til sidst blev kendt som x86 -familien. (En anden reference er, at PCI -leverandør -id'et til Intel -enheder er 8086 timer .)

detaljer

Busser og drift

Alle interne registre samt interne og eksterne databusser er 16 bit brede, hvilket fastgjorde "16-bit mikroprocessor" -identiteten for 8086. En 20-bit ekstern adressebus giver et 1 MB fysisk adresserum (2 20 = 1.048.576). Dette adresserum adresseres ved hjælp af intern segmentering "segmentering". Databussen er multiplekset med adressebussen for at passe alle kontrollinjerne til en standard 40-pin dobbelt in-line pakke . Det giver en 16-bit I/O-adressebus, der understøtter 64 KB separat I/O-rum. Det maksimale lineære adresserum er begrænset til 64 KB, simpelthen fordi interne adresse-/indeksregistre kun er 16 bit brede. Programmering over 64 KB hukommelsesgrænser indebærer justering af segmentregistre (se nedenfor); denne vanskelighed eksisterede, indtil 80386- arkitekturen introducerede bredere (32-bit) registre (hukommelsesstyringshardwaren i 80286 hjalp ikke i denne henseende, da dens registre stadig kun er 16 bit brede).

Hardware -tilstande

Nogle af styrepindene, der bærer essentielle signaler til alle eksterne operationer, har mere end én funktion, afhængigt af om enheden betjenes i min- eller max -tilstand. Den tidligere tilstand er beregnet til små enkeltprocessorsystemer, mens sidstnævnte er til mellemstore eller store systemer, der bruger mere end én processor (en slags multiprocessortilstand). Maksimal tilstand er påkrævet ved brug af en 8087 eller 8089 coprocessor. Spændingen på pin 33 (MN/ MX ) bestemmer tilstanden. Ændring af tilstanden for pin 33 ændrer funktionen af visse andre pins, hvoraf de fleste har at gøre med, hvordan CPU'en håndterer (lokal) bussen. Tilstanden er normalt hardwired i kredsløbet og kan derfor ikke ændres af software. Funktionerne i disse tilstande er beskrevet i form af tidsdiagrammer i Intel -datablade og manualer. I minimumstilstand genereres alle styresignaler af selve 8086.

Registre og instruktioner

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

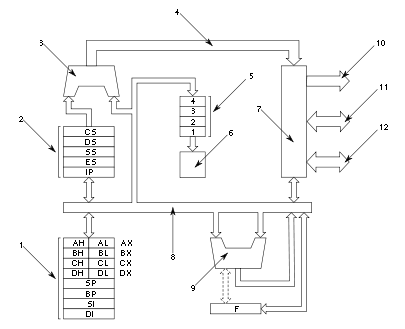

8086 har otte mere eller mindre generelle 16-bit registre (inklusive stakemarkøren, men eksklusive instruktionsmarkøren, flagregistret og segmentregistre). Fire af dem, AX, BX, CX, DX, kan også fås som dobbelt så mange 8-bit registre (se figur), mens de fire andre, SI, DI, BP, SP, kun er 16-bit.

På grund af en kompakt kodning inspireret af 8-bit processorer er de fleste instruktioner en-adresse eller to-adresse operationer, hvilket betyder, at resultatet er gemt i en af operanderne. Højst en af operanderne kan være i hukommelsen, men denne hukommelsesoperand kan også være destinationen , mens den anden operand, kilden , enten kan være registreret eller umiddelbar . En enkelt hukommelseslokation kan også ofte bruges som både kilde og destination, hvilket blandt andre faktorer yderligere bidrager til en kodetæthed, der kan sammenlignes med (og ofte bedre end) de fleste otte-bit-maskiner på det tidspunkt.

Generalitetsgraden for de fleste registre er meget større end i 8080 eller 8085. 8086 registre var imidlertid mere specialiserede end i de fleste nutidige minicomputere og bruges også implicit af nogle instruktioner. Selvom det er helt fornuftigt for samlingsprogrammereren, gør dette registerallokering til kompilatorer mere kompliceret i forhold til datidens mere ortogonale 16-bit og 32-bit processorer som PDP-11 , VAX , 68000 , 32016 osv. På den anden side Da det er mere regelmæssigt end de ret minimalistiske, men allestedsnærværende 8-bit mikroprocessorer som 6502 , 6800 , 6809 , 8085 , MCS-48 , 8051 og andre moderne akkumulatorbaserede maskiner, er det betydeligt lettere at konstruere en effektiv kodegenerator til 8086 -arkitekturen.

En anden faktor for dette er, at 8086 også introducerede nogle nye instruktioner (ikke til stede i 8080 og 8085) for bedre at understøtte stakbaserede programmeringssprog på højt niveau som Pascal og PL/M ; nogle af de mere nyttige instruktioner er og ret størrelse , der understøtter "Pascal -kaldekonventionen " direkte. (Flere andre, såsom og , blev tilføjet i de efterfølgende 80186, 80286 og 80386 processorer.)

push mem-op push immedenter

En stak på 64 KB (ét segment) , der vokser mod lavere adresser, understøttes i hardware ; 16-bit ord skubbes ind på stakken, og toppen af stakken peges på af SS: SP. Der er 256 afbrydelser , som kan påberåbes af både hardware og software. Afbrydelserne kan kaskade ved hjælp af stakken til at gemme returadresserne .

8086 har 64 K med 8-bit (eller alternativt 32 K med 16-bit ord) I/O-portplads .

Flag

8086 har et 16-bit flagregister . Ni af disse tilstandskodeflag er aktive og angiver processorens aktuelle tilstand: Bær flag (CF), Paritetsflag (PF), Hjælpeflag (AF), Nulflag (ZF), Tegnflag (SF), Trap flag (TF), Afbryd flag (HVIS), Retningsflag (DF) og Overløbsflag (OF). Flagregisterets layout kaldes også statusordet og er som følger:

| Bit | 15-12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Flag | AF | DF | HVIS | TF | SF | ZF | AF | PF | CF |

Segmentering

Der er også fire 16-bit segmentregistre (se figur), der giver 8086 CPU'en adgang til en megabyte hukommelse på en usædvanlig måde. I stedet for at sammenkoble segmentregistret med adresseregisteret, som i de fleste processorer, hvis adresserum overstiger deres registerstørrelse, forskyder 8086 16-bit segmentet kun fire bits tilbage, før det tilføjes til 16-bit offset (16 × segment + offset ), og producerer derfor en 20-bit ekstern (eller effektiv eller fysisk) adresse fra 32-bit segmentet: offset-par. Som følge heraf kan hver ekstern adresse refereres til af 2 12 = 4096 forskellige segment: offset par.

| 0110 1000 1000 0111 0000 | Segment , | 16 bit, skiftet 4 bit tilbage (eller ganget med 0x10) |

| + 0011 0100 1010 1001 | Forskydning , | 16 bits |

| 0110 1011 1101 0001 1001 | Adresse , | 20 bits |

Selvom den betragtes som kompliceret og besværlig af mange programmører, har denne ordning også fordele; et lille program (mindre end 64 KB) kan indlæses startende med en fast forskydning (f.eks. 0000) i sit eget segment, hvilket undgår behov for flytning , med højst 15 bytes justeringsaffald.

Kompilatorer til 8086 -familien understøtter normalt to typer markører , nær og fjernt . Nær pegepinde er 16-bit forskydninger implicit forbundet med programmets kode eller datasegment og kan derfor kun bruges inden for dele af et program, der er lille nok til at passe i et segment. Fjernpunkter er 32-bit segment: offsetpar, der løser til 20-bit eksterne adresser. Nogle kompilatorer understøtter også enorme pointers, som er som langt pointers, bortset fra at pointer-aritmetik på en enorm pointer behandler det som en lineær 20-bit pointer, mens pointer-aritmetik på en langt pointer ombrydes inden for sin 16-bit offset uden at røre segmentdelen af adressen.

For at undgå behovet for at angive nær og fjernt på talrige pointers, datastrukturer og funktioner understøtter kompilatorer også "hukommelsesmodeller", der angiver standardmarkørstørrelser. De små (maks. 64K), små (maks. 128K), kompakte (data> 64K), mellemstore (kode> 64K), store (kode, data> 64K) og enorme (individuelle arrays> 64K) modeller dækker praktiske kombinationer af nær , langt og enorme tip til kode og data. Den lille model betyder, at kode og data deles i et enkelt segment, ligesom i de fleste 8-bit baserede processorer, og kan f.eks. Bruges til at bygge .com- filer. Forkompilerede biblioteker findes ofte i flere versioner, der er kompileret til forskellige hukommelsesmodeller.

Ifølge Morse et al.,. designerne overvejede faktisk at bruge et 8-bit skift (i stedet for 4-bit) for at oprette et 16 MB fysisk adresserum. Da dette imidlertid ville have tvunget segmenter til at begynde på 256-byte grænser, og 1 MB blev betragtet som meget stort for en mikroprocessor omkring 1976, blev ideen afvist. Der var heller ikke nok stifter til rådighed på en billig 40-benet pakke til de yderligere fire adressebusstifter.

I princippet adressen plads af x86-serien kunne have været udvidet i senere processorer ved at øge skift værdi, så længe applikationer opnået deres segmenter fra operativsystemet og ikke gøre antagelser om ligestilling af forskellige segment: offset par. I praksis var brugen af "enorme" pointers og lignende mekanismer udbredt, og den flade 32-bit adressering blev muliggjort med 32-bit offset-registre i 80386 til sidst udvidet det begrænsede adresseringsområde på en mere generel måde (se nedenfor).

Intel kunne have besluttet at implementere hukommelse i 16 bit ord (hvilket ville have elimineret BHE -signalet (Bus High Enable) sammen med mange af adressebuskomplekserne, der allerede er beskrevet). Dette ville betyde, at alle instruktionsobjektkoder og data skulle tilgås i 16-bit enheder. Brugere af 8080 for længst indså i bakspejlet, at processoren udnytter sin hukommelse meget effektivt. Ved at have et stort antal 8-bit objektkoder producerer 8080 objektkoden lige så kompakt som nogle af de mest kraftfulde minicomputere på markedet dengang.

Hvis 8086 skal beholde 8-bit objektkoder og dermed den effektive hukommelsesbrug af 8080, kan den ikke garantere, at (16-bit) opcoder og data vil ligge på en lige-ulige byte adressegrænse. Den første 8-bit opcode vil flytte den næste 8-bit instruktion til en ulige byte eller en 16-bit instruktion til en ulige-byte grænse. Ved at implementere BHE- signalet og den ekstra logik, der er nødvendig, tillader 8086 instruktioner at eksistere som 1-byte, 3-byte eller andre ulige byte-objektkoder.

Kort sagt: dette er en afvejning. Hvis hukommelsesadressering er forenklet, så der kun er adgang til hukommelse i 16-bit-enheder, vil hukommelsen blive brugt mindre effektivt. Intel besluttede at gøre logikken mere kompliceret, men brug af hukommelse mere effektiv. Dette var på et tidspunkt, hvor hukommelsesstørrelsen var betydeligt mindre og med en præmie, end den, som brugerne er vant til i dag.

Portning af ældre software

Små programmer kunne ignorere segmenteringen og bare bruge almindelig 16-bit adressering. Dette gør det muligt at overføre 8-bit software ganske let til 8086. Forfatterne til de fleste DOS- implementeringer udnyttede dette ved at tilbyde et applikationsprogrammeringsinterface, der meget ligner CP/M , samt inkludere det simple .com- eksekverbare filformat, identisk til CP/M. Dette var vigtigt, da 8086 og MS-DOS var nye, fordi det gjorde det muligt hurtigt at gøre mange eksisterende CP/M (og andre) applikationer tilgængelige, hvilket i høj grad lettede accept af den nye platform.

Eksempel kode

Den følgende 8086/8088 assembler -kildekode er for en underrutine, der navngiver _memcpy, og kopierer en blok med databyte af en given størrelse fra et sted til et andet. Datablokken kopieres en byte ad gangen, og databevægelsen og looping-logikken anvender 16-bit operationer.

0000:1000 0000:1000 0000:1000 55 0000:1001 89 E5 0000:1003 06 0000:1004 8B 4E 06 0000:1007 E3 11 0000:1009 8B 76 04 0000:100C 8B 7E 02 0000:100F 1E 0000:1010 07 0000:1011 8A 04 0000:1013 88 05 0000:1015 46 0000:1016 47 0000:1017 49 0000:1018 75 F7 0000:101A 07 0000:101B 5D 0000:101C 29 C0 0000:101E C3 0000:101F |

; _memcpy(dst, src, len)

; Copy a block of memory from one location to another.

;

; Entry stack parameters

; [BP+6] = len, Number of bytes to copy

; [BP+4] = src, Address of source data block

; [BP+2] = dst, Address of target data block

;

; Return registers

; AX = Zero

org 1000h ; Start at 0000:1000h

_memcpy proc

push bp ; Set up the call frame

mov bp,sp

push es ; Save ES

mov cx,[bp+6] ; Set CX = len

jcxz done ; If len = 0, return

mov si,[bp+4] ; Set SI = src

mov di,[bp+2] ; Set DI = dst

push ds ; Set ES = DS

pop es

loop mov al,[si] ; Load AL from [src]

mov [di],al ; Store AL to [dst]

inc si ; Increment src

inc di ; Increment dst

dec cx ; Decrement len

jnz loop ; Repeat the loop

done pop es ; Restore ES

pop bp ; Restore previous call frame

sub ax,ax ; Set AX = 0

ret ; Return

end proc

|

Ovenstående kode bruger BP (basispeger) -registret til at etablere en opkaldsramme , et område på stakken, der indeholder alle parametre og lokale variabler til udførelse af underprogrammet. Denne form for opkaldskonvention understøtter reentrant og rekursiv kode, og har været brugt af de fleste ALGOL-lignende sprog siden slutningen af 1950'erne.

Ovenstående rutine er en ret besværlig måde at kopiere blokke af data på. 8086 indeholder dedikerede instruktioner til kopiering af byte -strenge. Disse instruktioner forudsætter, at kildedataene er gemt på DS: SI, destinationsdataene er gemt på ES: DI, og at antallet af elementer, der skal kopieres, er gemt i CX. Ovenstående rutine kræver, at kilden og destinationsblokken er i det samme segment, derfor kopieres DS til ES. Sløjfeafsnittet i ovenstående kan erstattes af:

0000:1011 FC 0000:1012 F3 0000:1013 A4 |

cld ; Copy towards higher addresses

loop rep ; Repeat until CX = 0

movsb ; Move the data block

|

Dette kopierer datablokken en byte ad gangen. Den REPinstruktion bevirker følgende MOVSBtil gentagelse indtil CX er nul, automatisk forøgelse SI og DI og decrementing CX som det gentager. Alternativt kan MOVSWinstruktionen bruges til at kopiere 16-bit ord (dobbeltbytes) ad gangen (i hvilket tilfælde CX tæller antallet af kopierede ord i stedet for antallet af bytes). De fleste montører genkender REPinstruktionen korrekt, hvis de bruges som et in-line præfiks til MOVSBinstruktionen, som i REP MOVSB.

Denne rutine fungerer korrekt, hvis den afbrydes, fordi programtælleren fortsat vil pege på REPinstruktionen, indtil blokkopien er fuldført. Kopien fortsætter derfor fra hvor den sluttede, da afbrydelsesrutinen returnerer kontrollen.

Ydeevne

Selvom den delvis er skygge af andre designvalg i denne særlige chip, begrænser den multipleksede adresse og databusser ydelsen lidt; overførsler af 16-bit eller 8-bit mængder udføres i en fire-timers hukommelsesadgangscyklus, som er hurtigere på 16-bit, selvom det er langsommere på 8-bit mængder, sammenlignet med mange nutidige 8-bit baserede CPU'er. Da instruktioner varierer fra en til seks bytes, hentes og eksekveres samtidigt og afkobles til separate enheder (som det forbliver i dagens x86-processorer): Busgrænsefladeenheden føder instruktionsstrømmen til eksekveringsenheden gennem en 6-byte prefetch-kø ( en form for løst koblet rørledning ), fremskynde operationer på registre og umiddelbare , mens hukommelsesoperationer blev langsommere (fire år senere blev dette ydelsesproblem løst med 80186 og 80286 ). Den fulde (i stedet for delvis) 16-bit arkitektur med ALU i fuld bredde betød imidlertid, at 16-bit aritmetiske instruktioner nu kunne udføres med en enkelt ALU-cyklus (i stedet for to, via intern transport, som i 8080 og 8085) , fremskynder sådanne instruktioner betydeligt. Kombineret med ortogonaliseringer af operationer kontra operandtyper og adresseringstilstande samt andre forbedringer, gjorde dette præstationsgevinsten over 8080 eller 8085 temmelig signifikant, på trods af tilfælde, hvor de ældre chips kan være hurtigere (se nedenfor).

| instruktion | registrere-registrere | registrere øjeblikkeligt | register-hukommelse | hukommelsesregister | hukommelses-øjeblikkelig |

|---|---|---|---|---|---|

| mov | 2 | 4 | 8+EA | 9+EA | 10+EA |

| ALU | 3 | 4 | 9+EA, | 16+EA, | 17+EA |

| hoppe | registrere ≥ 11; mærke ≥ 15; tilstand, etiket ≥ 16 | ||||

| heltal multiplicere | 70 ~ 160 (afhængig af operanddata data samt størrelse) herunder enhver EA | ||||

| heltal divider | 80 ~ 190 (afhængig af operanddata data samt størrelse) herunder enhver EA | ||||

- EA = tid til at beregne effektiv adresse, der spænder fra 5 til 12 cyklusser.

- Tidspunkter er bedst, afhængigt af status for forhåndshentning, instruktionstilpasning og andre faktorer.

Som det fremgår af disse tabeller, var operationer på registre og umiddelbare hurtige (mellem 2 og 4 cyklusser), mens instruktioner og spring fra hukommelsesoperand var ret langsomme; spring tog flere cyklusser end på den simple 8080 og 8085 , og 8088 (brugt i IBM PC) blev yderligere hæmmet af den smallere bus. Årsagerne til, at de fleste hukommelsesrelaterede instruktioner var langsomme, var tredobbelte:

- Løst koblede hente- og eksekveringsenheder er effektive til instruktionsforhentning, men ikke til spring og tilfældig dataadgang (uden særlige foranstaltninger).

- Der blev ikke givet nogen dedikeret adresseberegningsadder; mikrokode -rutinerne skulle bruge hoved -ALU'en til dette (selvom der var et dedikeret segment + offset adder).

- Adresse- og databusserne blev multiplekset , hvilket tvang en lidt længere (33 ~ 50%) buscyklus end i typiske nutidige 8-bit processorer.

Imidlertid blev ydeevnen til hukommelsesadgang drastisk forbedret med Intels næste generation af 8086 -familie -CPU'er. De 80186 og 80286 begge havde dedikeret adresse beregning hardware, hvilket sparer mange cykler, og 80.286 havde også separat (ikke-multiplex) adresse og data busser.

Flydende punkt

8086/8088 kunne forbindes til en matematisk coprocessor for at tilføje hardware/mikrokode-baseret floating-point ydeevne. Den Intel 8087 var standard matematik coprocessor for 8086 og 8088, der opererer på 80-bit-tal. Producenter som Cyrix (8087-kompatible) og Weitek ( ikke 8087-kompatible) kom til sidst med højtydende floating-point-coprocessorer, der konkurrerede med 8087.

Chip -versioner

Urfrekvensen var oprindeligt begrænset til 5 MHz, men de sidste versioner i HMOS blev specificeret til 10 MHz. HMOS-III- og CMOS- versioner blev fremstillet i lang tid (mindst et stykke tid ind i 1990'erne) til indlejrede systemer , selvom dens efterfølger, 80186 / 80188 (som indeholder nogle periferiudstyr på chip), har været mere populær til integreret brug .

80C86, CMOS -versionen af 8086, blev brugt i GRiDPad , Toshiba T1200 , HP 110 og endelig Lunar Prospector 1998–1999 .

Til emballagen var Intel 8086 tilgængelig både i keramiske og plastiske DIP -pakker.

Liste over Intel 8086

| Model nummer | Frekvens | Teknologi | Temperaturområde | Dato for frigivelse | Pris (USD) |

|---|---|---|---|---|---|

| 8086 | 5 MHz | HMOS | 0 ° C til 70 ° C | 8. juni 1978 | $ 86,65 |

| 8086-1 | 10 MHz | HMOS II | Kommerciel | ||

| 8086-2 | 8 MHz | HMOS II | Kommerciel | Januar/februar 1980 | $ 200 |

| 8086-4 | 4 MHz | HMOS | Kommerciel | $ 72,50 | |

| I8086 | 5 MHz | HMOS | Industriel −40 ° C til +85 ° C | Maj/juni 1980 | $ 173,25 |

| M8086 | 5 MHz | HMOS | Militær klasse −55 ° C til +125 ° C | ||

| 80C86 | CMOS |

Derivater og kloner

Kompatible - og i mange tilfælde forbedrede - versioner blev fremstillet af Fujitsu , Harris / Intersil , OKI , Siemens , Texas Instruments , NEC , Mitsubishi og AMD . For eksempel var NEC V20 og NEC V30 parret hardware-kompatible med 8088 og 8086, selvom NEC lavede originale Intel-kloner henholdsvis μPD8088D og μPD8086D, men inkorporerede instruktionssættet fra 80186 sammen med nogle (men ikke alle) af 80186 hastighedsforbedringer, hvilket giver en drop-in-mulighed for at opgradere både instruktionssæt og behandlingshastighed uden at producenter behøver at ændre deres design. Sådanne relativt enkle og laveffekt 8086-kompatible processorer i CMOS bruges stadig i integrerede systemer.

Elektronikindustrien i Sovjetunionen var i stand til at replikere 8086 gennem både industrispionage og reverse engineering . Den resulterende chip, K1810VM86 , var binær og pin-kompatibel med 8086.

i8086 og i8088 var henholdsvis kernerne på de sovjetfremstillede pc-kompatible EC1831- og EC1832- desktops. (EC1831 er EF -identifikationen af IZOT 1036C og EC1832 er EF -identifikationen af IZOT 1037C, udviklet og fremstillet i Bulgarien. EC står for Единая Система.) Imidlertid havde EC1831 -computeren (IZOT 1036C) betydelige hardwareforskelle fra IBM PC -prototypen . EC1831 var den første PC-kompatible computer med dynamisk busstørrelse (US patent nr. 4.831.514). Senere blev nogle af EC1831-principperne vedtaget i PS/2 (US patent nr. 5.548.786) og nogle andre maskiner (britisk patentansøgning, publikation nr. GB-A-2211325, offentliggjort 28. juni 1989).

Sovjetisk klon K1810VM86

|

Understøt chips

- Intel 8237 : direkte hukommelsesadgang (DMA) controller

- Intel 8251 : universal synkron/asynkron modtager/sender med 19,2 kbit/s

- Intel 8253 : programmerbar intervaltimer, 3x 16-bit max 10 MHz

- Intel 8255 : programmerbar perifer grænseflade, 3x 8-bit I/O-ben bruges til printerforbindelse osv.

- Intel 8259 : programmerbar afbrydelsescontroller

- Intel 8279 : tastatur/displaycontroller, scanner en tastaturmatrix og displaymatrix som 7-seg

- Intel 8282 / 8283 : 8-bit lås

- Intel 8284 : urgenerator

- Intel 8286 / 8287 : tovejs 8-bit driver. I 1980 var både Intel I8286/I8287 (industriel kvalitet) version tilgængelig for US $ 16,25 i mængder på 100.

- Intel 8288 : buscontroller

- Intel 8289 : bus arbiter

- NEC µPD765 eller Intel 8272A : diskettecontroller

Mikrocomputere, der bruger 8086

- Den Intel Multibus -kompatible single -board computer ISBC 86/12 blev annonceret i 1978.

- Den Xerox Notetaker var en af de tidligste bærbare computer design i 1978 og brugte tre 8086 chips (som CPU, grafikprocessor, og I / O-processor), men aldrig trådt kommerciel produktion.

- Seattle Computer Products afsendte S-100 busbaserede 8086-systemer (SCP200B) allerede i november 1979.

- Den norske Mycron 2000, introduceret i 1980.

- En af de mest indflydelsesrige mikrocomputere af alle, IBM-pc'en , brugte Intel 8088 , en version af 8086 med en 8-bit databus (som nævnt ovenfor).

- Den første Compaq Deskpro brugte en 8086, der kører på 7,16 MHz, men var kompatibel med tilføjelseskort designet til 4,77 MHz IBM PC XT og kunne skifte CPU'en ned til den lavere hastighed (som også skiftede til en hukommelsesbusbuffer for at simulere 8088's langsommere adgang) for at undgå problemer med software timing.

- En 8 MHz 8086-2 blev brugt i AT&T 6300 PC (bygget af Olivetti , og kendt globalt under flere mærker og modelnumre), en IBM PC-kompatibel stationær mikrocomputer. M24 / PC 6300 har IBM PC / XT-kompatible 8-bit ekspansionsåbninger, men nogle af dem har en proprietær udvidelse, der giver hele 16-bit databussen til 8086 CPU (ligner konceptet til 16-bit slots i IBM PC AT , men forskellig i designdetaljerne og fysisk inkompatibel), og alle systemudstyr inklusive det indbyggede videosystem nyder også 16-bit dataoverførsler. Den senere Olivetti M24SP bød på en 8086-2, der kører på fuldt maksimum 10 MHz.

- Den IBM PS / 2 modeller 25 og 30 blev bygget med en 8 MHz 8086.

- Amstrad PC1512 , PC1640 , PC2086, PC3086 og PC5086 brugte alle 8086 CPU'er ved 8 MHz.

- Den NEC PC-9801 .

- De Tandy 1000 SL-serien og RL maskiner anvendes 9,47 MHz 8086 CPU'er.

- Den IBM Displaywriter tekstbehandling maskine og Wang Professional Computer, fremstillet af Wang Laboratories , også brugt 8086.

- NASA brugte originale 8086 CPU'er på udstyr til jordbaseret vedligeholdelse af Space Shuttle Discovery indtil afslutningen af rumfærge-programmet i 2011. Denne beslutning blev truffet for at forhindre software regression, der kan opstå som følge af opgradering eller fra at skifte til ufuldkomne kloner.

- KAMAN proces- og områdestrålingsmonitorer

Se også

- Transistortælling

- iAPX , for iAPX -navnet

Noter

Referencer

eksterne links

- Intel datablade

- Liste over 8086 CPU'er og deres kloner på CPUworld.com

- 8086 Pinouts

- Maksimal tilstandsgrænseflade

- 8086 -brugermanualen oktober 1979 INTEL Corporation ( PDF -dokument)

- 8086 programkoder ved hjælp af emu8086 (Version 4.08) Emulator

- Intel 8086/80186 emulator skrevet i C, denne fil er en del af en større pc -emulator

-

Shirriff, Ken (juni 2020). "Et kig på matricen i 8086 -processoren" .

- - (juni 2020). "Die shrink: Hvordan Intel nedskalerede 8086 -processoren" .

- - (juli 2020). "Intel 8086 -processorens registre: fra chip til transistorer" .

- - (august 2020). "Omvendt konstruktion af huggormen inde i Intel 8086" .

- - (august 2020). "Omvendt konstruktion af 8086's aritmetiske/logiske enhed fra billederne" .